## 第十二章 80386微处理器

- ■80386的系统结构

- 80386的指令系统

- ■80386的存储器扩展

- ■80386的输入/输出接口

- 80386的异常和中断及其处理

- RISC简介

80386是INTE公司继80286之后推出的产品,是32位微处理器。80386微处理器内含275 000个晶体管,多任务设计,能同时执行多个程序。80386是Intel高档微处理器的基础,

## 12.1 80386系统结构

## 一、80286内部结构简介

80386CPU是32位微处理器。数据总线和地址总线均为32根,可直接寻址4GB物理地址空间。

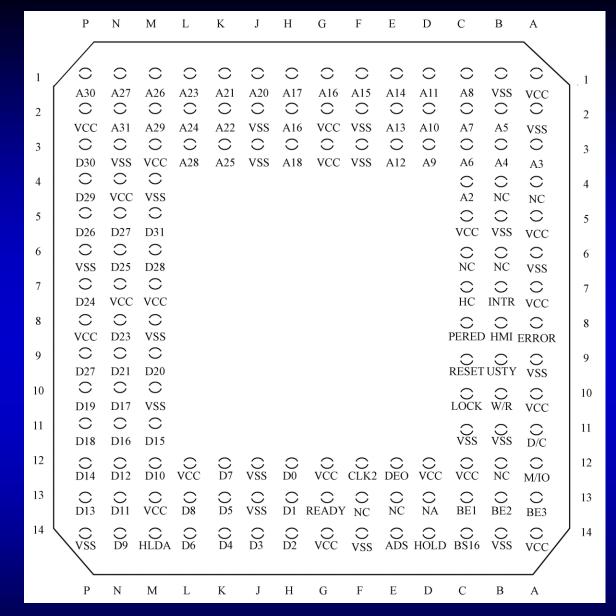

80386CPU封装,注意地址线和数据线是分开的

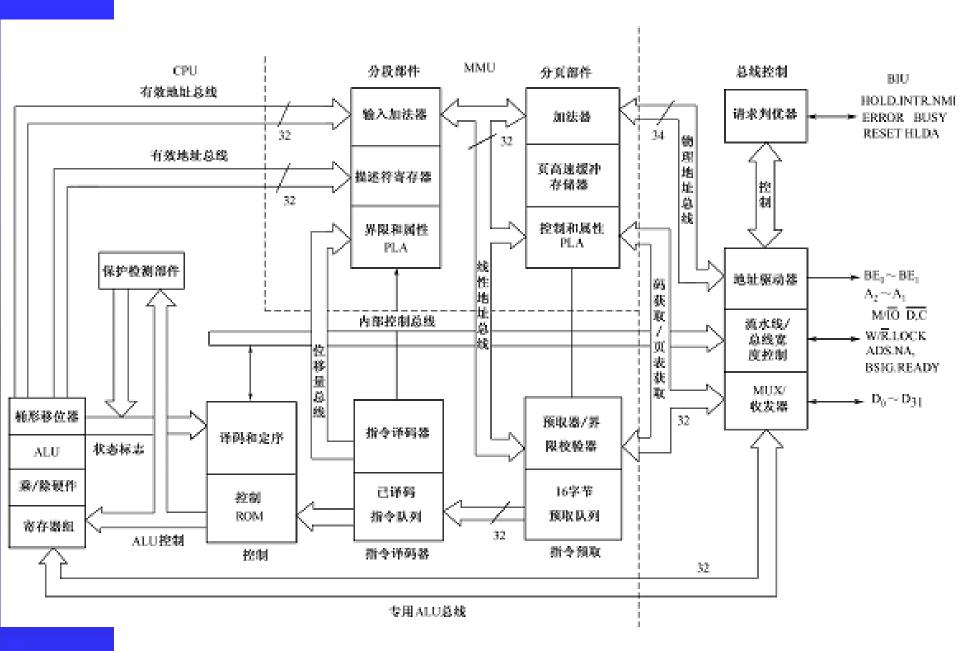

80386由三大部件组成:中央处理部件、总线接口部件和存储管理部件。

Intel 80386的基本体系结构

■ 1、中央处理部件(CPU, Central Process Unit)

CPU包括指令预取部件(IPU, Instruction Prefetch Unit), 指令译码部件(IDU, Instruction Predecode Unit), 执行部件(EU, Execution Unit)。

■ 2、总线接口部件(BIU, Bus Interface Unit)

BIU为CPU和系统之间的连接提供高速接口,其功能是产生访问存储器和I/O端口所必需的地址和命令信号等。

■ 3、存储器管理部件(MMU, Memory Management Unit)

MMU包含分段部件(SU, Segmentation Unit),分页部件(PU, Paging Unit)。SU能实现有效地址的计算,完成从逻辑地址到线性地址的转换,同时完成总线周期分段的违法检查。PU提供对物理地址空间的管理,通过两级页面重定位机构,把由SU产生的线性地址转换成物理地址。若不使用PU,80386的线性地址即为物理地址。

- a、总线接口部件BIU通过系统总线同外部联系,它从存储管理部件MMU接受已被选中的地址,而当IPU中的16个字节的指令预取队列有部分空字节时,BIU就会去访问存储器,读出后续指令并填充指令预取队列。

- b、预取队列中的指令代码送入中央处理部件 CPU的IDU,经指令译码器译码后,可按指令 的执行顺序进入已译码的指令队列,其中可存 放三条已译码的指令,它们排队等待进入EU去 执行。

■ c、EU所需要的原始数据来自BIU,而经过运 算所得的结果将送回给寄存器或存储单元。由 EU运算所求得的有关寻址信息送入MMU。

## 二、80386的存储器管理

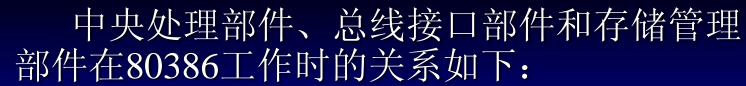

80386有三种工作模式:实地址模式、保护虚地址方式和虚拟8086模式。

## 实地址模式

在实地址模式下可把80386作为一个 高速的8086来使用,当80386加电或复位 后,就进入实地址工作模式。

实地址模式下的物理地址生成

## 保护虚地址方式

保护虚地址方式是80386处理器的主要工作模式。在保护虚地址方式下,支持内存分页机制,提供了对虚拟内存的良好支持。另外,在保护虚地址方式下,80386处理器和80286一样,支持优先级机制。

在保护虚地址方式下80386所有的32 根地址线都可供寻址,物理寻址空间高 达4 GB

## 虚拟8086模式

这是既有保护功能又能执行8086代码的工作模式。采用和保护虚地址方式相同的工作原理,但在程序中指定的逻辑地址可以和8086一样进行解释。在这种模式下,运行8086程序就像在8086CPU上运行一样。

虚拟86模式是为了在保护虚地址方式下 执行8086程序而设置的,其内存的寻址 方式和8086相同,也是可以寻址1MB的空 间。

## 三、保护虚地址方式下存储器管理

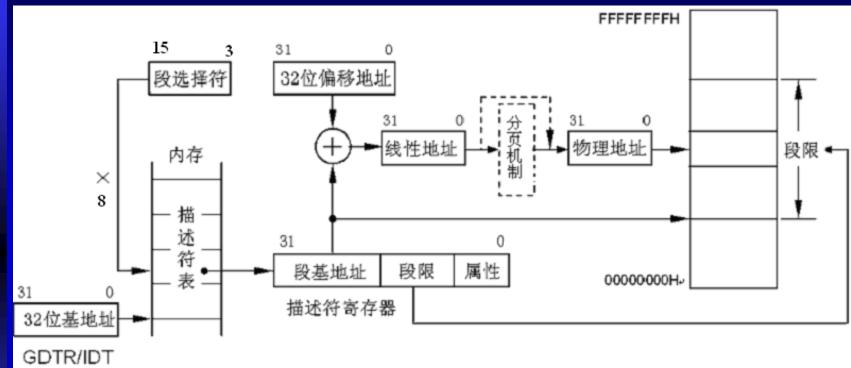

地址转换过程:

- 1、由段寄存器储存的内容就是段选择符,段选择符的高13位有效、低三位设为0作为偏移量,再以CPU内部预先初始化好的GDTR中的内容作为基地址,就可获得相应的描述符。该描述符将存入CPU中描述符寄存器中。

- 2、描述符中的段基地址(32位),同指令给出的 32位偏移地址相加得到线性地址。

- 3、如果分页,再通过分页机构进行变换,最后得到物理地址。如果不分页,线性地址就等于物理地址。

保护虚地址方式下的地址变换

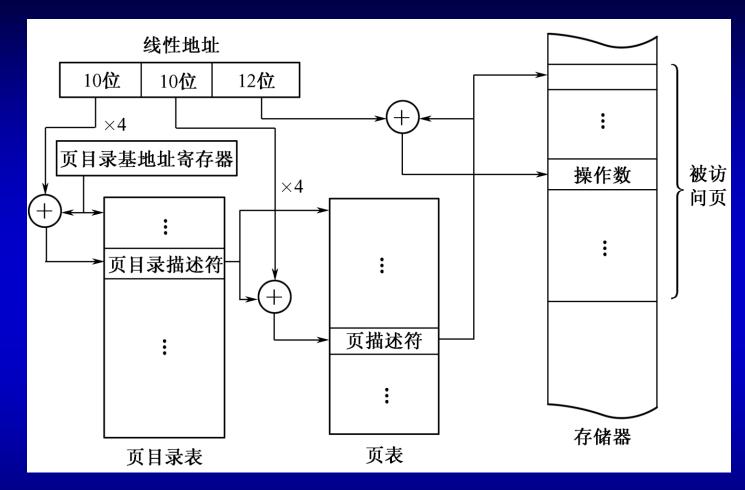

### 80386分页机制

在80386体系中,定义4K字节为一页,并规定每页的 开始地址都能被4K整除,即页地址在4K字节的边界上对 齐,这样4G字节的线性地址空间就划分成了220个页面。 80386分页机制管理的对象就是这些空间大小为一页的 存储块,它把整个线性地址空间和整个物理地址空间都 看成是由页组成的,线性地址中的任何一页都可以映射 到物理地址空间中的任何一页。

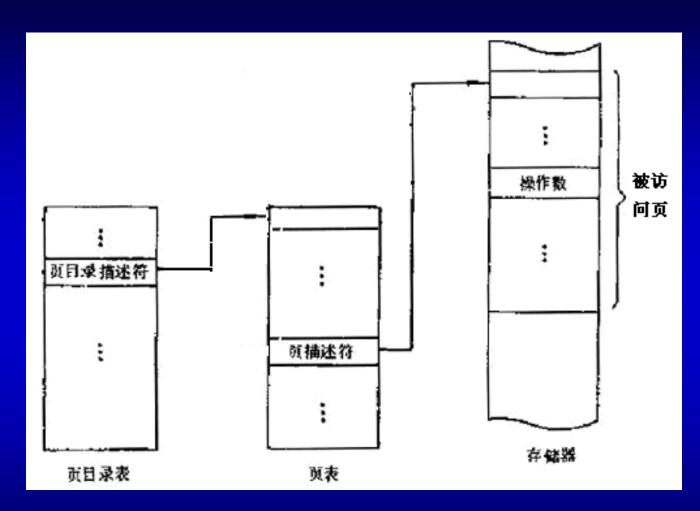

80386采用了两级页表结构来实现分页机制

寻址到某个页的页内存储单元一般要通过如下步骤:

- 1、首先通过段描述符获得32值段基址. 它与虚地址指示器中的32位偏移地址相加,得到32位线性地址。

- 2、把32位线性地址分成三个部分,前10位乘4指向页目录表的位移量、中间10位乘4指向页表的位移量,后12位是所寻址的操作数在页内的偏移地址。因此80386系统中的页目录表和页表可含有1K个项。每个项为32位,占4个字节,其中页目录表中的项就是页目录描述符,表示页表的首地址,页表中的项称为页描述符,表示操作数所在页的首地址。

3、由页目录表的位移量查表得页目录描述符的物理地址,由页目录描述符给出的页表首地址,结合页表的位移量查表得操作数所在页的首地址。页首地址和页内的偏移地址相加产生操作数的物理地址。

分页机制的寻址过程

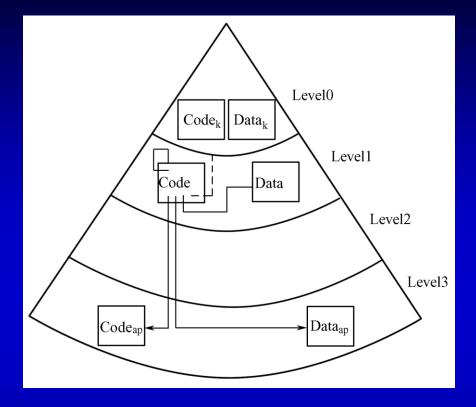

■四、80386的保护机制

80386采用保护机制主要为了检查和 防止低级别代码的越权操作,如访问不 该访问的数据、端口以及调用高优先级 的代码等。

特权级2访问的范围

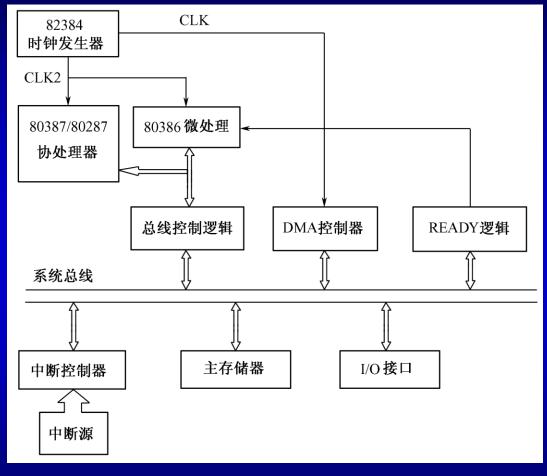

## 80386系统组成

80386的基本组成

# 12.2 80386的指令系统

一、 80386的寻址方式

全面兼容8086,同时增添如下寻址方式

- 1、带比例因子的变址寻址

- 2、带比例因子的基址变址寻址

- 3、带位移量,带比例因子的基址变址寻址

#### ■二、指令系统

◆1、数据传送指令

传送指令将字节、字、或者双字在寄存器与寄存器之间,寄存器与存储器之间,寄存器与存储器之间,存储器与存储器之间进行传送。这部分内容基本与8086一致与8086兼容,并增添32位操作,如

#### MOVSX EAX, BX

◆2、算术运算指令

算术运算指令包括加法、减法、乘法、 除法操作以及十进制加减法的结果调整等, 与8086的基本一样,

- ◆3. 位操作指令

- ♦ (1) 移位指令

32位移位指令

- ♦BT指令

- ◆BTS指令

- ◆BTC指令

- ◆BTR指令

- ♦BSF指令

- ◆BSR指令

- ◆ (1) 位串操作指令

- IBTS指令

- XBTS指令

- ◆ (2) 串输出指令

- OUTB/OUTW/OUTD指令

- ♦ (3) 串输入指令

- INSB/INSW/INSD指令

- ◆5. 程序控制转移指令 基本同8086一样

- ◆6. 处理器控制指令 基本同8086一样

- ◆ LMSW指令

- ◆ SMSW指令

- ◆ SIDT指令

- ◆ LGDT指令

- ◆ SGDT指令

- ◆ LLDT指令

- ◆ SLDT指令

- ◆ LTR指令

- ◆ STR指令

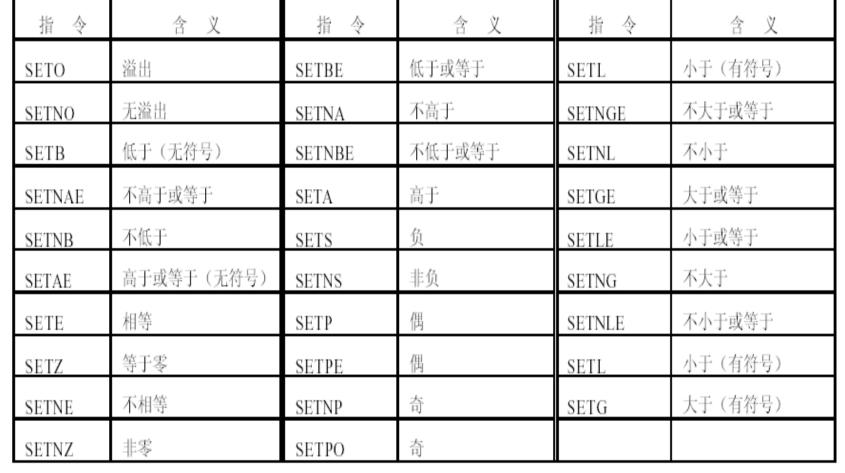

## ◆8. 条件设置字节指令

- ◆LAR指令为装入访问权限指令

- ◆LSL指令为装入段限制指令

- ◆VERR指令作用为验证段的可读性

- ◆VERW指令作用为验证段的可写性

- ◆ARPL指令作用为调整选择符的特权级。

- ◆BOUND指令作用为检查指定16位或 32位寄存器数值是否在第二操作数 所指定的两个存储器的界限内。

- ◆ENTER指令的作用是为过程参数建 立一个堆栈区

- ◆LEAVE指令的作用是撤销ENTER指 令的动作。

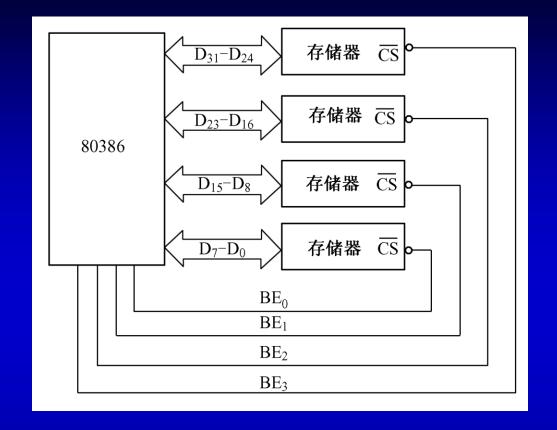

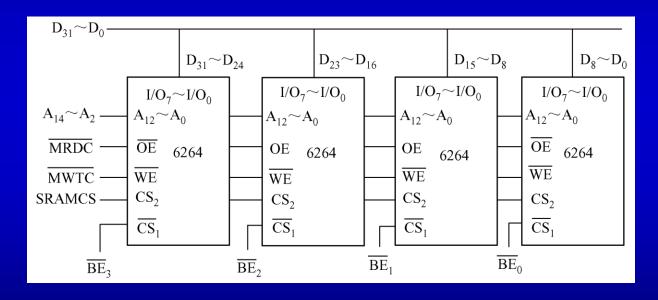

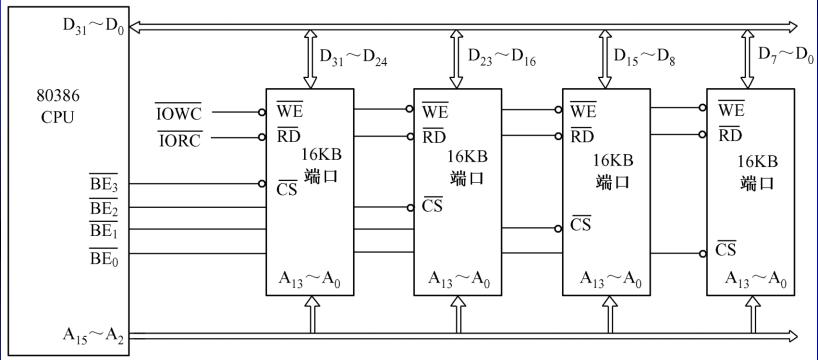

# 12.3 80386的存储器扩展

- ■一、基本的存储器接口控制线 80386 CPU提供的与存储器接口相关的 引脚主要有:

- ◆ D<sub>31</sub>~D<sub>0</sub> 数据线

- ◆ A<sub>31</sub>~A<sub>2</sub>地址总线

- ◆ /BE0~/BE3 字节控制线

- ◆ /BS16总线控制

- ◆ W/R、M/IO 等总线周期定义信号

字节使能信号的功能

## ■二、基本的存储器接口

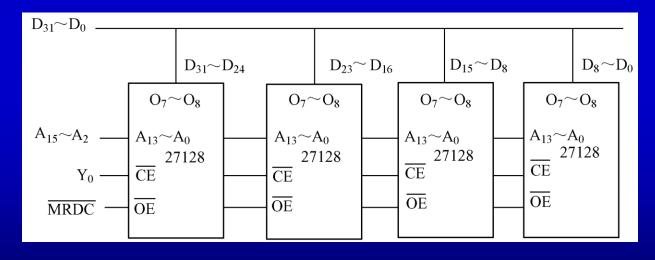

## ◆ 1. EPROM和80386接口

## ◆2. 静态RAM和80386接口

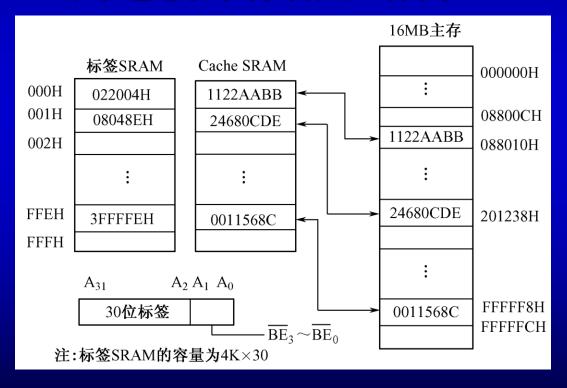

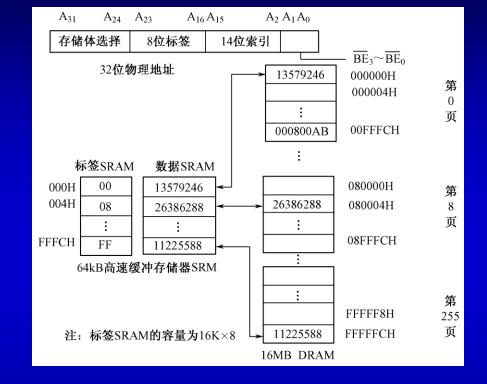

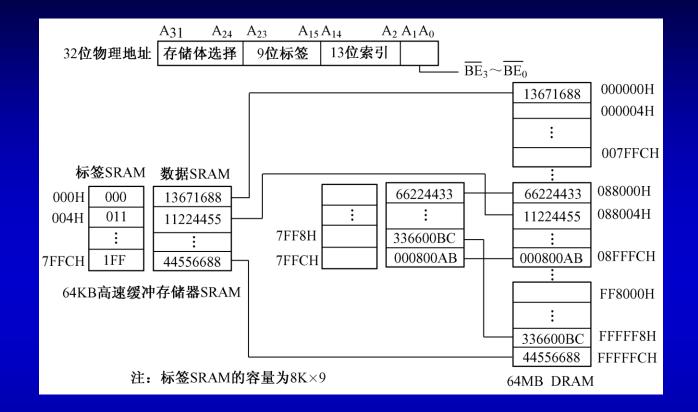

### ■三、高速缓冲存储器

高速缓冲存储器Cache是位于CPU与内存之间的临时存储器,它的工作速度数倍于主存,全部功能由硬件实现,并且对程序员是透明的。高速缓冲存储器的使用是为了解决CPU与内存存取速度不匹配的问题,即由于内存的存取速度低,从而影响了CPU的工作效率,利用Cache可以提高系统的工作效率。

### ◆1. 高速缓冲存储器结构

全关联高速缓冲存储器结构

双路组关联高速缓冲存储器结构

- ◆ (1) 高速缓存内容的更新

- 直写式系统

- 回写式系统

- ◆ (2) 高速缓存的一致性

- 总线监视

- 硬件透视

- 不可高速缓存的存储器

- 高速缓存卸出

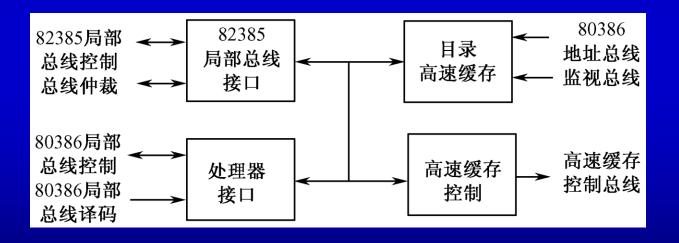

■ 四、Intel 82385高速缓存控制器

Intel 82385高速缓存控制器是Intel 80386高性能的外围接口芯片,集成了控制外部32KB的高速缓冲存储器所需的全部管理逻辑电路和高速缓冲目录存储器。

82385内部结构方框图

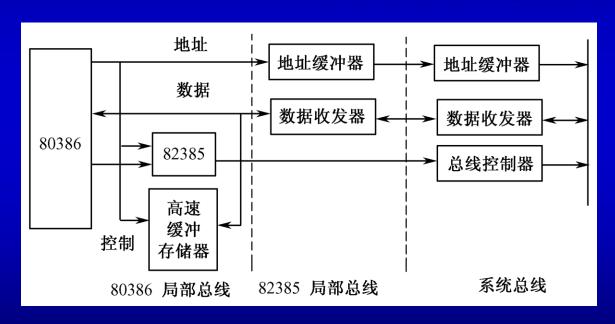

## ◆1、80386/82385系统的总线结构

80386/82385系统总线结构

- ◆主控模式

- ◆从模式

- ◆ 3、82385总线监视功能

# 12.4 80386的输入/输出接口

80386与8086的I/O接口几乎完全一样,接口芯片、I/O指令等全盘继承8086的体系,没有十分明显的变动和功能方面的提升。

#### 80386 I/O端口的物理组织

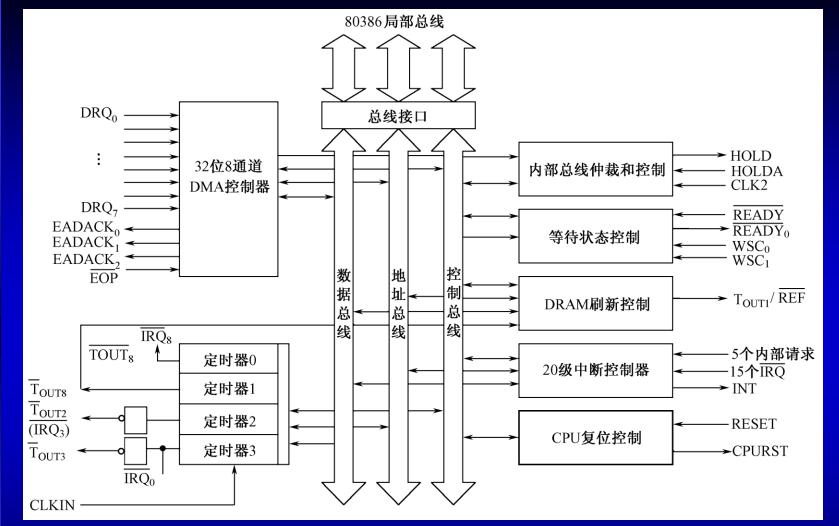

■ 多功能接口芯片82380

82380是专门为80386/80486系统设计的高性能多功能超大规模集成I/O接口芯片。从 I/O功能上看,它包括DMA控制器、中断控制器和定时器。除此之外,它还具有许多系统支援功能,如等待状态控制、DRAM刷新控制、系统复位控制等,因此又被称为集成系统外围支援器件。

82380系统结构功能图

#### 有如下功能

- ◆8个独立可编程DMA通道,允许使用32位总 线宽度

- ◆系统复位

- ◆20级可编程中断控制

- ◆4个16位可编程定时/计数器

- ◆ DRAM刷新控制

- ▶ 内部总线仲裁与控制

- ◆可编程等待状态控制

# 12.5 80386的异常和中断及其处理

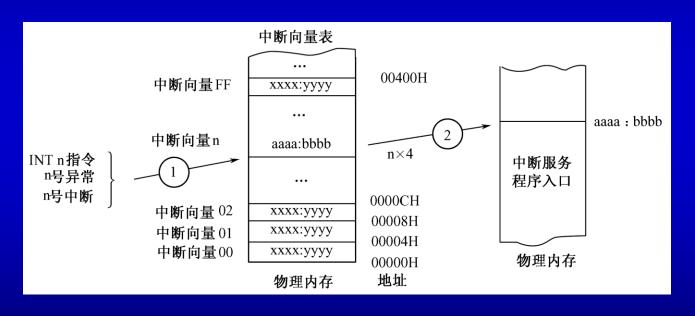

### ■一、实模式下异常和中断的处理过程

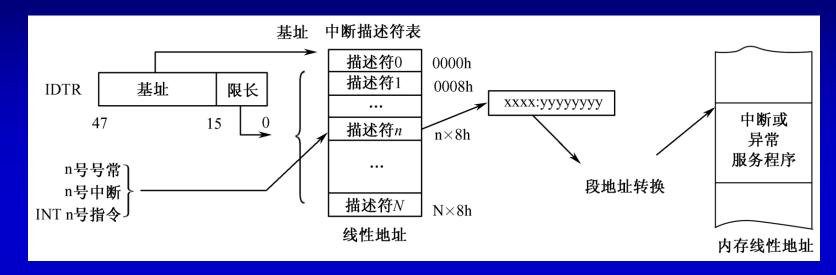

■二、保护虚地址方式下异常和中断的处理过程 在保护虚地址方式下,中断或异常处理往 往从用户代码切换到操作系统代码中执行。 于保护虚地址方式下的代码有优先级之分, 此出现了从优先级低的应用程序转移到优先级 高的系统代码中的问题,如果优先级低的代码 能够任意调用优先级高的代码,就相当于拥有 了高优先级代码的权限。为了使高优先级的代 码能够安全地被低优先级的代码调用,保护虚 地址方式下增加了"门"的概念。

保护虚地址方式下的中断和异常处理

- ◆异常种类

- ◆中断描述符表

- ◆中断响应和异常处理的步骤

# 12.6 精简指令集计算机(RISC)简介

- RISC的基本原理

- ■RISC的特色及其难点所在

- ■RISC的关键技术